# 6502 SOFTWARE Gourmet Guide & COOKBOOK

Put Together

Your Own 6502 Programs

Using These

Time-Tested Recipes

- General Purpose Routines

- Conversion Routines —

- Search and Sort Routines

- Floating Point Routines

- 6502 Instruction Set -

- And More -

# 6502 SOFTWARE Gourmet Guide & COOKBOOK

By Robert Findley

### Copyright © 1979 Scelbi Computer Consulting, Inc. Elmwood, CT 06110

### ALL RIGHTS RESERVED

### IMPORTANT NOTICE

No part of this publication may be reproduced, transmitted, stored in a retrieval system, or otherwise duplicated in any form or by any means electronic, mechanical, photocopying, recording or otherwise, without the prior express written consent of the copyright owner.

The information in this manual has been carefully reviewed, and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies or for the success or failure of various applications to which the information contained herein might be applied.

# **Foreword**

The "6502 Software Gourmet Guide & Cookbook" is written as an instructional publication for two audiences. First, it takes the BASIC language programmer into the realm of machine-language programming on the 6502. With the large number of computers on the market that use the 6502 as its central processor, one can find a new challenge by going one step closer to the inner workings of the CPU. There are many advantages to programming the 6502 at the machine-language level. This book presents these advantages in a way that a person with an introductory knowledge of computers will understand.

Second, the book is intended for the person with a knowledge of machine-language programming on a different CPU (i.e., 8080 or 6800) and wishes to become familiar with the 6502. The description of the 6502 structure and instruction set, along with the numerous applications discussed throughout the book, will quickly make an experienced programmer proficient with the 6502.

Robert Findley

November, 1979

# ACKNOWLEDGEMENT The author wishes to thank his wife, Barbara, and the staff at Scelbi for their invaluable help in preparing this book.

# **Contents**

Index Page 204

|   | Introduction Page 7                  |

|---|--------------------------------------|

| 1 | 6502 Instruction Set Page 9          |

| 2 | 6502 Programming Techniques Page 43  |

| 3 | General Purpose Routines Page 49     |

| 4 | Conversion Routines Page 71          |

| 5 | Floating Point Routines Page 91      |

| 6 | Decimal Arithmetic Routines Page 125 |

| 7 | Input/Output Processing Page 139     |

| 8 | Search and Sort Routines Page 169    |

|   | Appendices Page 192                  |

|   |                                      |

# Introduction

Have you tried cooking up a program lately on your 6502 microcomputer, and you just can't seem to get the right mixture of instructions? Or did that math recipe your friend gave you turn out to have too many bugs in it, and leave a sour taste in your mouth? Don't toss your computer in the sink and grind those bad listings up in the garbage disposal. Here's a book that will help take you from a novice that burns the bits to a gourmet chef that can make the sweetest APPLEcations program pie imaginable.

Before throwing together your favorite dish, a thorough know-ledge of the basic ingredients, namely the 6502 instruction set, is essential. Every chef that's worth his salt knows exactly what each ingredient will do for him. Begin creating your masterpiece by mixing in a little of this routine and a little of that routine. Spice up the program with a few of your own special application routines, and before baking, add a personal touch by folding in the input/output driver routines for the peripherals in your system. Bake thoroughly with your assembler, and there you have it! Your programming masterpiece, ready to feed into your computer's memory for hours of tasty enjoyment.

Is your taste for math routines? Or manipulating data tables and character strings? Or maybe you wish to do some real time programming. Or set up your system to operate the peripherals under interrupt control. Whatever your requirements may be, there is certain to be some ideas, techniques, and routines in this book to aid you in programming for your specific application.

## Chapter 1

# The 6502 Instruction Set

The instruction set of the 6502 CPU provides considerable programming power to the machine language programmer. There are 56 basic instructions which, when all permutations are considered, provide 151 individual instructions. These instructions use from one to three bytes of memory depending on the function they perform.

There are several basic elements in the structure of the 6502 CPU with which the programmer must become thoroughly familiar. These elements include the Program Counter, the Accumulator, the two Index Registers, the Stack Pointer, Memory, and the Status Flags. Also, an understanding of certain concepts is important. For instance, with the 6502, input and output operations are performed using the same instructions which access the memory. The numerous addressing modes provide a versatility for very creative programming. One should be knowledgeable of these elements and concepts before attempting to write machine language programs.

### The Internal Registers

The program counter is a sixteen-bit register which is used to direct the flow of a program from one instruction to another. Since the program counter is sixteen bits long, it can directly access instructions in any of the possible 64K bytes of memory. After an instruction is executed, the program counter is automatically incremented to the next location memory from which the next instruction to be executed will be taken. This automatic increment may be overridden if the current instruction directs the computer to a different memory location. In this case, the program counter is loaded with the new address, and a program execution continues with the instruction.

From the software point of view, the accumulator of the 6502 is the real workhorse element. All arithmetic and Boolean logic operations accumulate their results in this register. This eightbit register, designated by the letter A, is also used for intermediate storage when transferring data from one memory location to another. A number of instructions for shift, rotate and compare also may be performed with the content of the accumulator. The condition of the status flags is affected by almost every operation of the accumulator.

The index registers, designated as X and Y, perform three important functions. First, as their name implies, they are used to form pointers which index into the memory for data storage, retrieval, manipulation and examination. The contents of the index register are added to a base address to allow selection of a successive group of memory locations. This is accomplished simply by incrementing the index register. Since these registers are only eight bits wide, it may appear that the range of the index register is limited to 256. However, as will be discussed in Chapter 2, there are programming techniques to extend this range. Their second function is that of an eight-bit counter register. By incrementing or decrementing these registers with the appropriate instructions, they may be used to count up, or down, keeping track of the number of occurrences of a specific event or, possibly the passage of time. The final function is, as general purpose registers, to transfer data between memory locations and between registers.

The stack pointer is an eight-bit register used to index into page one of the memory for storing and retrieving data on the stack. The stack is the storage area in which the 6502 CPU saves the return addresses of subroutine calls and the pertinent data that must be stored when an interrupt occurs. The data is stored and retrieved from the stack in a push-pull manner. This method is discussed in greater detail later.

### **External Memory Structure**

The memory is the element in which the programs to be executed are stored. It also contains data that may be used by the programs. As mentioned earlier, the 6502 is capable of directly addressing up to 64K of memory. Each memory location consists of eight bits which together are referred to as a byte. The memory associated with any one individual system may vary. It may consist of a combination of ROM and/or PROM memories, which contain permanently stored programs or data. Or it could consist of a

RAM memory whose contents may be altered by the computer for storing various programs or data as needed.

The input/output structure of the 6502 allows the transfer of data to and from the peripheral interfaces by assigning memory addresses to the peripheral. By setting up memory locations as the channels through which data is transferred to and from the peripherals, it is possible to use any of the instructions that refer to the memory for transferring the I/O data. This affords the programmer great flexibility in testing the status and controlling the peripheral devices.

### The Status Flags

In order to make decisions based on the contents of a register or memory location, or the results of an arithmetic or logical operation, the 6502 offers four status flags. They are set to one (for a true condition), or cleared to zero (for a false condition), in accordance with the results of an operation performed. Not all status flags are affected by the execution of each instruction. Only those flags that have relevance are affected by an instruction. These status flags are referred to as carry (C), overflow (V), negative (N), and zero (Z). The flag condition may be tested by several instructions. The instructions' operation will vary as a consequence of the flags particular status at the time it is tested.

The carry flag may be considered an extension of the eight-bit accumulator, or a memory location, used as the operand of an instruction. For addition and subtraction operations, the carry is considered the ninth bit and will indicate when an addition causes an overflow from bit seven, or a subtraction requires a borrow for bit seven. By functioning in this manner, the carry flag becomes a necessary link when performing multiple-precision operations. The carry flag is also considered an extension of a register or memory location in various rotate and shift operations. There are a number of instructions that set up the carry to a given condition. This function may be necessary when executing a group of instructions that require the carry to be set initially to a known state.

The negative flag indicates the condition of the most significant bit of a register or memory location following the last instruction that affects the negative flag. If the result leaves the most significant bit set to one, the negative flag will be set to one. If the most significant bit is zero, the negative flag also will be zero. For example, if the contents in a memory location are added to the contents of accumulator A, and this results in the most significant bit

in accumulator A being set to one, the negative flag will be set to one. Or, if a memory location is rotated once to the right, moving a zero into the most significant bit, the negative flag will be cleared to zero as a result of the operation.

The overflow flag provides an indication of a two's complement overflow as a result of an addition or subtraction. For addition, the two's complement overflow occurs when bit seven of both addends is the same value and bit seven of the sum is the opposite value (the addition of two negative numbers equaling a positive value). For subtraction, a two's complement overflow occurs when bit seven of the subtrahend and minuend are opposite, and bit seven of the result takes on the value of bit seven of the subtrahend (the subtraction of a negative from a positive number with a negative result).

The zero flag is set to one when the execution of an instruction results in an all-zero value. This may occur following an arithmetic or Boolean logic operation. It may also occur after an index register or memory location has been incremented or decremented to zero.

### **Condition Flags**

In addition to the status flags, there are also three condition flags which are controlled either by execution of specific instructions or by certain hardware functions. These flags are designated the interrupt disable flag (I), the break flag (B) and the decimal mode flag (D).

The interrupt disable flag is used to indicate when the maskable interrupt input is disabled. When the flag is set to one, the maskable interrupt input is disabled. The CPU will not respond to an interrupt on this line. When this flag is cleared, an interrupt on the maskable interrupt line will be acknowledged by the CPU. This flag is set upon receipt of any one of the three interrupts. Upon returning from the interrupt, it is restored to its initial condition at the time the interrupt was received. It may also be set or cleared by the execution of two instructions that perform these specific functions.

The break flag is used to indicate the execution of a software interrupt. It is set when the break instruction is executed and reset after the status register is stored on the stack as a result of the BREAK instruction. The status register then may be examined to determine whether the interrupt was generated by hardware or software. A more detailed description of the BREAK instruction and flag will be presented later.

The decimal mode flag controls the type of arithmetic addition

or subtraction to be performed. These two types are decimal and binary addition and subtraction. The decimal mode assumes that the numbers to be added or subtracted are in BCD (binary coded decimal) form before the operation. The result is presented in BCD form. The binary mode assumes both values are in binary representation before and after the operation. This flag is set to one for decimal arithmetic and cleared to zero for binary arithmatic by two specific instructions. This flag allows one to write a single group of subroutines to perform both decimal and binary mathematic functions.

### Combining All the Flags

These seven flags are arranged in an eight-bit register. The flags are combined so that they may be stored and retrieved easily for interrupt operations.

This register is called the STATUS register. The flags are assigned the following bit locations. One should note that the unused bit (bit 5) either may be set or cleared at any time and therefore should be ignored when working with the status register.

|       |   | Status Register Bit Definition |   |

|-------|---|--------------------------------|---|

| Bit 0 | _ | Carry Flag                     | С |

| Bit 1 | - | Zero Flag                      | Z |

| Bit 2 | _ | Interrupt Disable              | 1 |

| Bit 3 | - | Decimal Mode                   | D |

| Bit 4 | - | Break Flag                     | В |

| Bit 5 | _ | Unused                         |   |

| Bit 6 | _ | Overflow Flag                  | ٧ |

| Bit 7 | _ | Negative Flag                  | Ν |

### How the Stack Operates

The stack is used to store and retrieve data in the memory locations on page one indicated by the stack pointer. The stack pointer operates in a push-pull manner. Its operation is the same whether the data being stored is (1) a return address from a subroutine call, (2) the return address and status register at the time of an interrupt, (3) the storage or retrieval of the contents of the accumulator. When data is stored in the stack, the data byte is stored in the memory location indicated by the stack pointer. The stack pointer then is automatically decremented. If more than one byte is to be stored, as in the storage of a return address, each additional byte is loaded into the memory. The stack pointer is decremented following each

byte storage. By automatically decrementing the stack pointer in this manner, it is positioned to store more data or read data stored in the stack when either a pull instruction or a return from subroutine, or interrupt, is executed. The following illustrates the method of storing the return address of a subroutine call in the stack. The return address to be stored is location \$5E on page 02.

### **Before Subroutine Call**

| Stack<br>Pointer<br>\$FF | Memory Address<br>of Stack<br>\$1FD<br>\$1FE<br>\$1FF | Stack<br>Contents<br>\$00<br>\$00<br>\$00 |

|--------------------------|-------------------------------------------------------|-------------------------------------------|

| \$FD                     | After Subroutine Call<br>\$1FD<br>\$1FE<br>\$1FF      | , \$00<br>\$5E<br>\$02                    |

By performing a return or pull instruction when data is read from the stack, the reverse procedure is followed. That is, the stack pointer is automatically incremented and the data byte is read from the stack. The stack pointer is now positioned for the next stack operation, whether it be to read or write data in the stack.

### The Format of Interrupt Operations

The 6502 CPU has provisions for three types of interrupts. Two interrupts are generated by hardware, the third is an interrupt created by a software instruction. The CPU responds to each of these interrupts by storing the return address and the status register in the stack and setting the interrupt disable flag. The CPU then selects the interrupt vector according to the type of interrupt received. This interrupt vector is actually a start address for an interrupt service routine. In most cases, this interrupt service routine begins in ROM memory with several short instructions that fetch another address set up in the RAM memory by the programmer. This second address would be the start of the actual interrupt service routine written to operate the devices associated with one's system.

The first of the hardware interrupts is called the nonmaskable interrupt. This interrupt, when received, will always be acknowl-

edged by the CPU. It is often used by high speed devices that have a very short time to transfer data. Or, it may be used by powerloss detect circuits to allow the CPU time to shutdown critical operations. Also, it can retain current operating status before the power falls to inoperable levels. The nomaskable interrupt is assigned its own interrupt vector.

The other hardware interrupt is called the maskable interrupt. The CPU responds to the receipt of a maskable interrupt by the setting of the interrupt disable flag. As previously discussed, when this flag is reset, the CPU will acknowledge a maskable interrupt. If this flag is set to one, the CPU will ignore this hardware interrupt. This allows the programmer to control when the program can and cannot respond to a maskable interrupt. This interrupt shares its vector with the software interrupt.

A software interrupt is generated by the execution of the software interrupt instruction. The 6502 reacts in the same fashion as it would to a nonmaskable interrupt. However, the software interrupt is not maskable by the interrupt disable flag. It will always vector to the interrupt service routine. Since the maskable and software interrupts share the same vector, it is necessary for the interrupt service routine to examine the contents of the status register stored in the stack to determine which type of interrupt was received. The break flag will be set for a software interrupt.

The use of interrupts in a microcomputer system allows a program to be performing one function while waiting for a peripheral device to complete its operation. For example, a mailing list program could be sorting out names of people living in a specific geographical area, while a printer device, operating under interrupt control, prints the selected names.

There is also a RESET interrupt which is generally used to direct the CPU to a start-up program. The reset is simply an overriding interrupt that halts execution of any program currently running and directs control to a program which may reinitialize the hardware to a known state. A separate vector is assigned for the reset interrupt.

The interrupt vectors are set up in the hardware at the highest addressable locations of the computer (FFFA to FFFF). As discussed, these vectors direct the CPU to specific memory locations when the respective interrupts occur. The page portion of the vector address is in the higher address, and the low portion of the vector is in the lower address of each vector. The vectors are arranged in memory as follows:

Address of Vector FFFF,FFFE FFFD,FFFC FFFB,FFFA Type of Interrupt

Software and maskable

RESET

Nonmaskable interrupt

### Addressing Modes Add Variety

The 6502 instruction set makes extensive use of various AD-RESSING modes. These different modes of addressing provide many instructions with up to eight ways of selecting the instructions operand. The addressing mode may refer to the location that contains (or is to receive) data for the instruction execution. Or, it may refer to the location of the next instruction to be executed. The instructions that use these different addressing modes require an additional one or two bytes of memory to be properly defined by the actual machine code.

The first byte of the instruction contains the machine code which indicates the instruction to be executed along with the addressing mode used for that instruction. The information contained in the additional bytes of the instruction would indicate either the actual data to be used as the operand, the location in memory where the data is (or will be) stored, or a relative address. These addressing modes are referred to as immediate, zero page, zero page indexed, absolute, absolute indexed, indexed indirect, indirect indexed and relative.

The source listing of the instructions that use these modes is separated into two fields. The first is called the operator field, and contains the mnemonic for the operation to be performed. The second field is the operand field which will indicate the addressing mode to be used for the instruction. As will be pointed out later, when the individual instructions are presented, the machine code for the same mnemonic will vary depending on the addressing mode selected.

Whenever a numeric value is designated as the operand of the source listing for an instruction, the value will be represented by hexadecimal digits. In order to conform with the generally accepted notation for representing hexadecimal values in the source listing, these values will be preceded by a dollar sign (\$). For example, an instruction to load the accumulator from memory location 00A7 will appear as follows: LDA \$00A7.

### **Immediate Addressing Mode**

The immediate addressing mode selects the operand from the

memory location following the first byte of the instruction. The instructions that allow the immediate mode of addressing require two bytes. The first byte contains the machine code for the operation to be performed and the second byte contains the immediate data value that will be used. The listings contained in this text have the operand preceded by a pound sign (#) whenever the immediate addressing mode is used. The following example illustrates the execution of the instruction that loads the accumulator with the immediate value of ten (hexadecimal):

### Before Execution

Contents of A = XX (don't care)

### Instruction Executed

Source code LDA #\$10 Machine code \$A9 \$10

### After Execution

Contents of A = \$10

### Zero Page Addressing Mode

The zero page addressing mode selects the operand of the instruction from a memory location on page 00. This mode requires one additional byte to specify the location on page 00 to be used by the instruction. It is advantageous to use page 00 for the storage of frequently used data. This allows one to access the specific location on page 00 with a two-byte instruction, rather than using an additional byte to specify the page, as in the absolute mode.

The example below illustrates the execution to store the accumulator instruction using the zero-page addressing mode. The instruction in the example stores the contents of the accumulator in memory location 49 (hexadecimal).

### Before Execution

Contents of A = \$85

Contents of memory location \$0049 = XX (don't care)

### Instruction Executed

Source code STA \$49 Machine code \$85 \$49

### After Execution

Contents of A = \$85

Contents of memory location \$0049 = \$85

### Zero-Page Indexed Addressing Mode

The zero-page indexed addressing mode is similar to the zero-

page addressing mode in that the operand refers to a specific location on page 00. However, the actual memory location is selected by adding the contents of the X index register to the operand value. The X index register thus becomes an offset from the location indicated by the operand. One should note two points. First, the Y index is only valid in this mode when loading or storing the page 00. If the sum of the operand plus the index register exceeds \$FF, the overflow is ignored and the instruction loops back to the beginning of page 00.

The following example illustrates the execution of ANDing the accumulator with the third entry in a table which begins on page 00, location \$50.

### **Before Execution**

Contents of A = \$47

Contents of X = \$02

Contents of memory location \$0050 = \$01

Contents of memory location \$0051 = \$02

Contents of memory location \$0052 = \$04

Contents of memory location \$0053 = \$08

### Instruction Executed

Source code AND \$50.X Machine code \$35 \$50

### After Execution

Contents of A = \$04

### **Absolute Addressing Mode**

The absolute addressing mode uses two additional bytes to define the address of the memory location used as the operand for the instruction. The first of these two bytes contains the lower portion of the memory address; the second contains the page portion. Thus, the absolute mode allows one to directly access any memory location in the system for use as the operand of the instruction. When instructions that allow both absolute and zero-page addressing modes are assembled, the distinction between the two is determined by the page number of the address. If the page number is zero, the zero-page addressing mode should be selected. If the page number is not zero, the absolute addressing mode must be used.

The following example illustrates the execution of the load,

the accumulator with the contents of a memory location using the absolute addressing mode. The contents of memory location \$0280 are loaded into the A accumulator.

### **Before Execution**

Contents of A = XX (don't care)

Contents of memory location \$0280 = \$67

### Instruction Executed

Source code LDA \$0280 Machine code \$AD \$80 \$02

### After Execution

Contents of A = \$67 Contents of memory location \$0180 = \$67

### **Absolute Indexed Addressing Mode**

The absolute indexed addressing mode uses the operand address stored in the two bytes following the machine code for the instruction, and adds the contents of the X or Y index register to determine the actual memory location used by the instruction. The operand is stored with the first byte containing the lower portion of the memory address and the second byte containing the page portion. Unlike the zero-page indexed mode, this mode will cross a page boundary if the sum of the low portion of the operand and the index register is greater than \$FF. Note that the X and Y index registers may be used in most instructions that allow absolute indexed addressing.

The following example adds the contents of the memory location following location \$0520 to the accumulator, using the Y index register.

### **Before Execution**

Contents of A = \$20

Contents of Y = \$01

Contents of memory location \$0520 = \$15

Contents of memory location \$0521 = \$30

Contents of memory location \$0522 = \$45

Carry flag is reset

### Instruction Executed

Source code ADC \$0520,Y Machine code \$79 \$20 \$05

### After Execution

Contents of A = \$50

### **Indirect Addressing Mode**

The next three addressing modes utilize a common form of addressing known as indirect addressing. It uses an intermediate storage area to store a pointer. This pointer indicates the actual memory location used with the instruction. The operand of the instruction calls out the location of the intermediate pointer. This indirect method of fetching an operand allows a fixed instruction sequence to operate on numerous memory locations by simply changing the intermediate pointer. These modes used in the 6502 use page zero for storing the intermediate pointer. Therefore, the indirect addressing instructions only require two memory locations: the first to store the machine code for the instruction, and the second to store the location on page zero at which the pointer will be found. The pointer is stored in two consecutive bytes with the low portion of the address stored in the first byte and the page position stored in the second byte.

The indirect addressing mode is used by the JUMP instruction to select the location of the next instruction to be executed. The address stored as the pointer on page zero is moved into the program counter and the program sequence shifts to the routine beginning at this new address.

### **Indexed Indirect Addressing Mode**

The indexed indirect addressing mode uses the X index register to offset the instruction operand. The content of the index register is added to the instruction operand. This value then is used to fetch the pointer on page zero which is in turn used to indicate the memory location operated on by the instruction. This instruction allows one to set up a table of pointers on page zero and, by manipulating the X index register, the desired pointer will be selected. It should be noted that if the sum of the operand plus the X index register is greater than \$FF, the result will wrap around to the beginning of page zero.

The following example illustrates the operation of the indexed indirect addressing mode. The accumulator is stored in a memory location which is indexed indirectly through a pointer on page zero.

### **Before Execution**

Contents of A = \$55

Contents of X = \$02

Contents of memory location \$0080 = \$24

Contents of memory location \$0081 = \$05

Contents of memory location \$0082 = \$22

Contents of memory location \$0083 = \$05

Contents of memory location \$0522 = \$XX (don't care)

Contents of memory location \$0524 = \$XX (don't care)

### Instruction Executed

Source code STA (\$80,X) Machine code \$81 \$80

### After Execution

Contents of A = \$55

Contents of memory location \$0522 = \$55

Contents of memory location \$0524 = \$XX (don't care)

### **Indirect Indexed Addressing Mode**

The indirect indexed addressing mode offsets the value of the pointer selected from page zero by adding the Y index register to it. The instruction operand indicates the location of the pointer on page zero. The contents of the Y index register is added to this pointer to select the actual memory location to be operated on. Thus, a table of as many as 256 entries may be set up in any section of the memory with a pointer to its lowest address stored on page zero. By proper adjustment of the Y index register, any desired entry in the table may be selected. This method is illustrated below. This example loads the accumulator with the second entry of a table beginning at location \$0400.

### **Before Execution**

Contents of A = XX

Contents of Y = \$01

Contents of memory location \$0090 = \$00

Contents of memory location \$0091 = \$04

Contents of memory location \$0400 = \$B1

Contents of memory location \$0401 = \$B2

Contents of memory location \$0402 = \$B3

### Instruction Executed

Source code LDA (\$90).Y Machine code \$B1 \$90

### After Execution

Contents of A = \$B2

### **Relative Addressing Mode**

The relative addressing mode references a memory location relative to the current value of the program counter +2. The relative addressing mode is used exclusively by the branch instructions. Two bytes are required to define the branch instruction. The first byte of the branch instruction calls out which conditional branch is to be executed. The second byte contains the relative displacement in two's complement form. Branching to a memory location is calculated by simply adding the second byte to the value of the program counter +2. If the most significant bit is a one, the branch will be to an address lower than the current program counter +2. A value of zero for the most significant bit indicates a branch to a higher address. The two's complement notation limits the branch instructions to a displacement of -128 to +127 locations from the value of the program counter +2.

If the zero flag is set, the following example illustrates a branch back to the instruction located \$0E hexadecimal locations before the branch instruction.

### **Before Execution**

Program counter = \$0270 (Location of first machine code of branch)

### Instruction Executed

Source code BEQ \$F0 Machine code \$F0 \$F0

### After Execution

Program counter = \$0262

Described here are the various types of instructions available with the 6502 CPU and will provide the mnemonic name used for writing programs in symbolic language. The machine code for the instruction is given as two hexadecimal digits. In cases where the mnemonic allows more than one addressing mode, the additional machine codes are listed, followed by an indication of the addressing mode to which they relate. Appendix A contains a list of these mnemonics and machine codes in alphabetical order. These mnemonics are equivalent to those defined by MOSTEK. Information concerning the timing for the instructions is also included.

The use of mnemonics facilitates working with an assembler program when developing relatively large and complex programs.

Thus, the programmer is urged to concentrate on learning the mnemonics for the instructions, and not to memorize the machine codes. After a program has been written using the mnemonics, the programmer can use a lookup table for conversion to machine code if an assembler program is not available.

The following discussion of the 6502 instruction set is preceded by the mnemonics and machine code in either two or three columns. The first column contains the mnemonic representation of the instruction. The second column contains the machine code for that mnemonic. In cases where several addressing modes are possible, the third column indicates the addressing mode for the machine code.

The first group of instructions loads data from the accumulator to the memory, and vice versa. These instructions require one to three bytes of memory.

### Load the Accumulator from Memory

| LDA | #DATA    | \$A9 | IMMEDIATE         |

|-----|----------|------|-------------------|

| LDA | ADDR     | \$A5 | ZERO PAGE         |

| LDA | ADDR,X   | \$B5 | ZERO PAGE INDEXED |

| LDA | ADDR     | \$AD | ABSOLUTE          |

| LDA | ADDR,X   | \$BD | ABSOLUTE INDEXED  |

| LDA | ADDR,Y   | \$B9 | ABSOLUTE INDEXED  |

| LDA | (ADDR,X) | \$A1 | INDEXED INDIRECT  |

| LDA | (ADDR),Y | \$B1 | INDIRECT INDEXED  |

This group of instructions loads the accumulator with the content of the memory location indicated by the addressing mode. For the immediate mode, the instruction requires two bytes and the data to be loaded into the accumulator is taken from the second byte of the instruction. For the zero-page modes, the instruction requires two bytes, with the second byte indicating the location onpage 00 from which the data is to be taken and loaded into the accumulator. The second and third bytes of the three-byte absolute mode instruction contain the low and page portion of the address from which the data to be loaded is taken. The indirect modes require two bytes. The second byte indicates the location on page zero containing the indirect pointer. The N and Z flags are affected as a result of these instructions. The C, I, D and V flags remain unchanged.

### Store Accumulator in Memory

| STA | ADDR   | \$85 | ZERO PAGE         |

|-----|--------|------|-------------------|

| STA | ADDR.X | \$95 | ZERO PAGE INDEXED |

| STA | ADDR     | \$8D | ABSOLUTE         |

|-----|----------|------|------------------|

| STA | ADDR,X   | \$9D | ABSOLUTE INDEXED |

| STA | ADDR,Y   | \$99 | ABSOLUTE INDEXED |

| STA | (ADDR,X) | \$81 | INDEXED INDIRECT |

| STA | (ADDR),Y | \$91 | INDIRECT INDEXED |

Storing data contained in the accumulator to a memory location is accomplished by the execution of one of these instructions. The exact location in memory is determined by the addressing mode used. The immediate mode is not valid for this instruction. The zero page and indirect modes require two bytes, and the absolute modes require three. The status flags are affected in a similar manner as loading the accumulator from the memory instructions.

# PUSH the Accumulator onto the Stack PHA \$48

This instruction stores the contents of the accumulator into the memory location indicated by the stack pointer. After storing the data, the stack pointer is automatically decremented to the proper position for the next stack operation. This one-byte instruction provides a convenient method for temporarily storing the contents of the accumulator without designating a specific memory location for its storage. None of the status flags are affected.

# PULL Data from the Stack into the Accumulator PLA \$68

Execution of this instruction first increments the stack pointer, and then transfers the data in the memory location indicated by the stack pointer to the designated accumulator. This instruction is used in conjunction with the push instruction to retrieve data pushed onto the stack. The status flags are not affected.

The next section contains instructions that deal with the loading, storing, and manipulation of the index registers contents and stack pointer. Proper manipulation of these registers is essential in programming the 6502 efficiently. The number of bytes required for this group of instructions varies from one to three.

### Load the Index Registers

| LDX | #DATA | \$A2 | IMMEDIATE |

|-----|-------|------|-----------|

| LDX | ADDR  | \$A6 | ZERO PAGE |

| LDX | ADDR,Y | \$B6 | ZERO PAGE INDEXED |

|-----|--------|------|-------------------|

| LDX | ADDR   | \$AE | ABSOLUTE          |

| LDX | ADDR,Y | \$BE | ABSOLUTE INDEXED  |

| LDY | #DATA  | \$A0 | IMMEDIATE         |

| LDY | ADDR   | \$A4 | ZERO PAGE         |

| LDY | ADDR,X | \$B4 | ZERO PAGE INDEXED |

| LDY | ADDR   | \$AC | ABSOLUTE          |

| LDY | ADDR,X | \$BC | ABSOLUTE INDEXED  |

This group of instructions load the designated index register from the memory location defined by the respective addressing modes. The immediate and zero page instructions require two bytes of memory and the absolute addressing mode requires three bytes. An index register is not used to load itself when an indexed addressing mode is called out. The resultant contents of the index register affect the N and Z flags, and the C, I, D and V flags are left unchanged.

### Store the Index Registers

| STX | ADDR   | \$86 | ZERO PAGE         |

|-----|--------|------|-------------------|

| STX | ADDR,Y | \$96 | ZERO PAGE INDEXED |

| STX | ADDR   | \$8E | ABSOLUTE          |

| STY | ADDR   | \$84 | ZERO PAGE         |

| STY | ADDR,X | \$94 | ZERO PAGE INDEXED |

| STY | ADDR   | \$8C | ABSOLUTE          |

Storing the contents of the designated index register is accomplished by the execution of one of these instructions. The contents of the index register remain unchanged. The zero-page addressing modes require two bytes of memory and the absolute mode requires three bytes. The flags are affected in the same manner as with the load index register instructions.

### Increment the Index Register

| INX | \$E8 |

|-----|------|

| INY | \$C8 |

These one byte instructions increment the designated index register by one. By using the index registers as part of a pointer, via an indexed addressing mode, this instruction is used to advance the pointer from one location to the next. The N and Z flags are affected while the C, I, D and V flags remain unchanged.

### **Decrement the Index Registers**

DEX \$CA DEY \$88

These instructions perform the opposite function of increment instructions. The contents of the designated index register is decremented by one. The N and Z flags reflect the result of the operation while the C, I, D and V flags are unchanged.

### Transfer from Accumulator to Index Register

TAX \$AA TAY \$A8

The current contents of the accumulator are transferred to the designated index register. This is a convenient one byte instruction for the temporary storage of the accumulator. The N and Z flags are affected by these instructions while the C, I, D and V flags and the contents of the accumulator remain unchanged.

### Transfer from Index Register to Accumulator

TXA \$8A TYA \$98

The contents of the designated index register are transferred to the accumulator. This may be performed to allow arithmetic or logical operations on the contents of the index register which can only be executed in the accumulator. As in the previous transfer instructions only the N and Z flags are affected by these one byte instructions.

### Transfer from Stack Pointer to the X Index Register

TSX \$BA

This one-byte instruction transfers the contents of the stack pointer to the X index register. The stack pointer maintains its initial contents following the execution. By loading the X index register with the address contained in the stack pointer, the absolute indexed addressing mode instructions may be used to store data on the stack while in a subroutine. Also, by incrementing the X index register following this instruction, an indexed pointer is set to examine and/or change the return address of a subroutine call. The N and Z flags are the only flags affected.

# Transfer from X Index Register to Stack Pointer TXS \$9A

This instruction transfers the contents of the X index register into the stack pointer. This one byte instruction is used to initialize the stack pointer at the start of a program. It may also be used to move the stack pointer to a new location in the stack, with the intent, possibly, of skipping a return address or some data stored on the stack. None of the status flags are affected by this instruction.

These instructions listed above describe the transfer of data between internal CPU registers, and a CPU register and a memory location. Several instructions that allow the manipulation of data within the CPU registers have also been discussed. The 6502 provides a similar type manipulation of memory contents. These instructions utilize the zero page and absolute modes of addressing, and require two or three bytes of memory.

| ı | ncrement | the | Memory | Location |

|---|----------|-----|--------|----------|

|   |          |     |        |          |

| INC | ADDR   | \$E6 | ZERO PAGE         |

|-----|--------|------|-------------------|

| INC | ADDR,X | \$F6 | ZERO PAGE INDEXED |

| INC | ADDR   | \$EE | ABSOLUTE          |

| INC | ADDR,X | \$FE | ABSOLUTE INDEXED  |

The designated memory location is incremented by one. The absolute addressing mode requires three bytes of memory, and the zero page requires two. This makes it convenient to set up a memory location as a pointer. Only the X index register is used in the indexed form. Only the N and Z flags are affected by the execution.

### **Decrement the Memory Location**

| DEC | ADDR   | \$C6 | ZERO PAGE         |

|-----|--------|------|-------------------|

| DEC | ADDR,X | \$D6 | ZERO PAGE INDEXED |

| DEC | ADDR   | \$CE | ABSOLUTE          |

| DEC | ADDR.X | \$DE | ABSOLUTE INDEXED  |

These instructions decrement the contents of the designated memory location by one. The X index register is used exclusively by the indexed form. As in the increment memory instructions, the zero page addressing mode requires two bytes and the absolute mode requires three bytes. The N and Z flags are conditioned to indicate the result and the C, I, D and V flags are left unchanged.

The following group of instructions allows the programmer to

direct the computer to perform arithmetic operations between the accumulator and the designated memory location. Also, there is a pair of instructions that control whether the arithmetic assumes binnary or BCD digits in the accumulator and memory location. The instructions in this group that use the immediate, zero page and indirect addressing modes require two bytes, and the absolute requires three.

### **Set the Decimal Mode** SED \$F8H

Addition and subtraction of two bytes in a computer normally assumes that the contents of the bytes are eight-bit binary values. However, this instruction allows one to store the data to be added or subtracted as BCD digits. A BCD digit is a four-bit binary number within the range of zero to nine. The six binary values above nine are invalid. This instruction sets the decimal mode flag. As long as this flag remains set, the execution of the addition and subtraction instructions assumes that the accumulator and memory location used contain two BCD digits. The result of the arithmetic operation leaves two BCD digits in the accumulator. This one-byte instruction affects only the decimal mode flag.

# Clear the Decimal Mode

All addition and subtraction instruction executed when the decimal mode flag is cleared assumes the data to be in binary form. Only the decimal mode flag is affected.

# Add the Contents of Memory Plus the Carry Flag

|     | to the Accumulator |              |                   |  |

|-----|--------------------|--------------|-------------------|--|

| ADC | #DATA              | \$69         | IMMEDIATE         |  |

| ADC | ADDR               | \$65         | ZERO PAGE         |  |

| ADC | ADDR,X             | \$75         | ZERO PAGE INDEXED |  |

| ADC | ADDR               | \$6D         | ABSOLUTE          |  |

| ADC | ADDR,X             | \$7D         | ABSOLUTE INDEXED  |  |

| ADC | ADDR,Y             | <b>\$</b> 79 | ABSOLUTE INDEXED  |  |

| ADC | (ADDR,X)           | \$61         | INDEXED INDIRECT  |  |

| ADC | (ADDR),Y           | \$71         | INDIRECT INDEXED  |  |

These instructions add the contents of the designated memory

location to the accumulator. The carry flag is also added to the least significant bit of the accumulator. The result of the addition is left in the accumulator in the format dictated by the decimal mode flag. The carry flag is the link between bytes when adding two multiple precision values. The N, Z and V flags are also updated to indicate the result of the addition. The contents of the memory location used are not changed.

# Subtract the Memory Contents and the Carry Flag from the Accumulator

| SBC | #DATA    | \$E9 | IMMEDIATE         |

|-----|----------|------|-------------------|

| SBC | ADDR     | \$E5 | ZERO PAGE         |

| SBC | ADDR,X   | \$F5 | ZERO PAGE INDEXED |

| SBC | ADDR     | \$ED | ABSOLUTE          |

| SBC | ADDR,X   | \$FD | ABSOLUTE INDEXED  |

| SBC | ADDR,Y   | \$F9 | ABSOLUTE INDEXED  |

| SBC | (ADDR,X) | \$E1 | INDEXED INDIRECT  |

| SBC | (ADDR),Y | \$F1 | INDIRECT INDEXED  |

The contents of the memory location and the carry flag are subtracted from the accumulator. The result of the subtraction either in binary or BCD, is stored in the accumulator and the carry flag will be reset if a borrow was required for the subtraction of the most significant bits. The N, Z and V flags are also affected by these instructions.

There is a group of instructions that perform a subtraction operation without altering the contents of any CPU registers or memory locations. However, the results of the subtraction operation are indicated by the condition of several of the status flags. The purpose of these instructions is to allow the program to compare the contents of the accumulator or index register to a value in memory.

The following group of compare instructions is very powerful and somewhat unique. They direct the computer to compare the contents of the designated accumulator or index register against the contents of the memory, and set the status flags as a result of the compare operation. Essentially it is a subtraction operation, with the value in the memory being subtracted from the value in the accumulator or index register. The value in the accumulator or index register is not altered by the operation. However, the flags are set in the same manner as though an actual subtraction operation had occurred. Subsequently, by testing the status of the various flags after a compare instruction is executed, the program can determine

whether the compare operation resulted in a match or not. The flags will indicate the relative magnitude of the two values with respect to each other.

These various tests are accomplished by utilizing the conditional branch instructions (to be described later). Unlike the SBC instructions, the carry flag is not included in the subtraction.

### Compare the Contents of the Memory to the Accumulator

| CMP | #DATA    | \$C9 | IMMEDIATE         |

|-----|----------|------|-------------------|

| CMP | ADDR     | \$C5 | ZERO PAGE         |

| CMP | ADDR,X   | \$D5 | ZERO PAGE INDEXED |

| CMP | ADDR     | \$CD | ABSOLUTE          |

| CMP | ADDR,X   | \$DD | ABSOLUTE INDEXED  |

| CMP | ADDR,Y   | \$D9 | ABSOLUTE INDEXED  |

| CMP | (ADDR,X) | \$C1 | INDEXED INDIRECT  |

| CMP | (ADDR),Y | \$D1 | INDIRECT INDEXED  |

|     |          |      |                   |

This group of compare instructions compares the content of the designated memory location to the content of the accumulator and requires two bytes for the immediate, zero page and indirect addressing modes, and three bytes for the absolute mode. The C, N and Z flags are conditioned according to the results of the subtraction operation. The V flag is not changed.

### Compare the Contents of the Memory to the Index Register

|     | •     |      | •         |

|-----|-------|------|-----------|

| CPX | #DATA | \$E0 | IMMEDIATE |

| CPX | ADDR  | \$E4 | ZERO PAGE |

| CPX | ADDR  | \$EC | ABSOLUTE  |

| CPY | #DATA | \$C0 | IMMEDIATE |

| CPY | ADDR  | \$C4 | ZERO PAGE |

| CPY | ADDR  | \$CC | ABSOLUTE  |

These instructions compare the contents of the designated index register with the memory location. The contents of the indicated memory location is subtracted from the index register. The C, N and Z flags are affected by the result of the subtraction. However, the V flag, memory location and index register remain unchanged. The immediate and zero-page addressing mode instructions require two bytes and the absolute mode instructions require three. These instructions are useful in testing for the end of a table pointed to by the index register.

There are several groups of instructions that allow Boolean logic

operations to be performed between the contents of locations in the memory and the accumulator. Boolean logic operations are valuable in a number of programming applications. The 6502 instruction set allows three basic Boolean operations to be performed. These are the logical AND, logical OR, and EXCLUSIVE OR operations. Each type of logic operation is performed on a bit-by-bit basis between the memory location and the accumulator specified by the instruction.

These instructions utilize four basic addressing modes to define the memory location to be used. For this entire group, the immediate, zero page and indirect mode instructions require two bytes of memory, while the absolute mode requires three.

| "AN | D" the | Accumi | ılator |

|-----|--------|--------|--------|

|     |        |        |        |

| AND | #DATA    | \$29 | IMMEDIATE         |

|-----|----------|------|-------------------|

| AND | ADDR     | \$25 | ZERO PAGE         |

| AND | ADDR,X   | \$35 | ZERO PAGE INDEXED |

| AND | ADDR     | \$2D | ABSOLUTE          |

| AND | ADDR,X   | \$3D | ABSOLUTE INDEXED  |

| AND | ADDR,Y   | \$39 | ABSOLUTE INDEXED  |

| AND | (ADDR,X) | \$21 | INDEXED INDIRECT  |

| AND | (ADDR),Y | \$31 | INDIRECT INDEXED  |

When the Boolean AND instruction is executed, each bit of the accumulator will be compared with the corresponding bit in the memory location specified by the instruction. As each bit is compared, a logic result will be placed in the accumulator. The logic result is determined as follows: If both the bit in the accumulator and the bit in the memory location with which the operation is being performed are a "1," the accumulator bit will be left as a "1." For other possible combinations (i.e., the accumulator bit = "0," and the memory location bit = "1," or if the accumulator bit = "1" and the memory contents bit = "0," or if both the accumulator and the memory contents have the particular bit = "0"), the accumulator bit will be set to "0." An example will illustrate the logical AND operation:

| Initial State of the Accumulator: | 10101010 |

|-----------------------------------|----------|

| Contents of Memory Location:      | 11001101 |

| Final State of the Accumulator:   | 10001000 |

The eight logical AND instructions perform this type of logic

operation between the accumulator and memory location, the result of the operation is stored in the accumulator. The N and Z flags are affected by the results of the logical AND operation. C and V flags are not affected.

| Logical "OR" the Accumulator |          |             |                   |

|------------------------------|----------|-------------|-------------------|

| ORA                          | #DATA    | \$09        | IMMEDIATE         |

| ORA                          | ADDR     | <b>\$05</b> | ZERO PAGE         |

| ORA                          | ADDR,X   | \$15        | ZERO PAGE INDEXED |

| ORA                          | ADDR     | \$0D        | ABSOLUTE          |

| ORA                          | ADDR,X   | \$1D        | ABSOLUTE INDEXED  |

| ORA                          | ADDR,Y   | \$19        | ABSOLUTE INDEXED  |

| ORA                          | (ADDR,X) | \$01        | INDEXED INDIRECT  |

| ORA                          | (ADDR),Y | \$11        | INDIRECT INDEXED  |

This group of Boolean logic instructions direct the computer to perform the logical OR operation on a bit-by-bit basis with the designated accumulator and contents of the memory location. The logical OR operation will result in the accumulator having a bit set to "1" if either the bit in the accumulator, or the corresponding bit in the memory location is a "1." Since the case where both the accumulator bit and the operand bit is a "1" also satisfies the relationship, that condition will also result in the accumulator bit being a "1." If neither accumulator nor memory location has a "1" in the bit position, the accumulator bit remains "0." An example illustrates the results of the logical OR operation:

| Initial State of the Accumulator: | 10101010 |

|-----------------------------------|----------|

| Contents of the Operand Register: | 11001101 |

| Final State of the Accumulator:   | 11101111 |

The logical OR instructions listed here perform this operation between the accumulator and memory location. The execution of these instructions leaves the result in the accumulator. The effect on the status flags is the same as for the logical AND instructions.

| Logical "EXCLUSIVE OR" the Accumulator |        |      |                   |  |

|----------------------------------------|--------|------|-------------------|--|

| EOR                                    | #DATA  | \$49 | IMMEDIATE         |  |

| EOR                                    | ADDR   | \$45 | ZERO PAGE         |  |

| EOR                                    | ADDR,X | \$55 | ZERO PAGE INDEXED |  |

| EOR                                    | ADDR   | \$4D | ABSOLUTE          |  |

| EOR                                    | ADDR,X | \$5D | ABSOLUTE INDEXED  |  |

| EOR | ADDR,Y   | <b>\$</b> 59 | ABSOLUTE INDEXED |

|-----|----------|--------------|------------------|

| EOR | (ADDR,X) | \$41         | INDEXED INDIRECT |

| EOR | (ADDR),Y | <b>\$</b> 51 | INDIRECT INDEXED |

This group of Boolean logic instructions is a variation of the logic OR. The variation is termed the logical EXCLUSIVE OR. The EXCLUSIVE OR operation is similar to the OR, except that when the corresponding bits in both accumulator and the operand register are a "1," the accumulator bit will be set to "0." Thus, the accumulator bit will be a "1" after the operation only if one of the registers has a "1" in the bit position. An example provides clarification:

| Initial State of the Accumulator: | 10101010 |

|-----------------------------------|----------|

| Contents of the Operand Register: | 11001101 |

| Final State of the Accumulator:   | 01100111 |

These logical EXCLUSIVE OR instructions, similar to those for the AND and OR, perform the operation between the accumulator and memory location with the results being stored in the accumulator. The status flags are also affected, or not affected, in the same manner as the logical AND instructions.

### **BIT Test Memory with the Accumulator**

| BIT | ADDR | \$24 | ZERO PAGE |

|-----|------|------|-----------|

| BIT | ADDR | \$2C | ABSOLUTE  |

The BIT test instruction tests one or more bits in a memory location without altering the contents of the memory location. This is accomplished by performing a logic AND between the accumulator and the memory location. Although neither alter their contents, the Z flag will indicate whether one or more common bit positions contain a "1." Testing for the condition of a particular bit is done by loading the accumulator with zeros in all bits except the one to be tested. This bit is loaded with a one. Executing BIT would set the Z flag to one if the bit in memory is zero, or clear the Z flag if it is one. The condition of bit 7 and bit 6 of the memory location is loaded directly into flags N and V respectively. This is done independently of the logic AND operation. Thus, one may test these two bits with the BIT instructions, without initializing the accumulator. The C flag is not affected. The zero page addressing mode requires two bytes to define the operation and the absolute mode requires three.

The 6502 has a group of instructions that allow the programmer to condition several of the status flags individually. The status register also may be stored and retrieved from the stack. All of the instructions in this group require only one byte of memory. The instructions that refer to an individual flag affect only that flag. All other status flags remain in their initial condition.

Set the Carry Flag SEC \$38

This instruction sets the carry flag to a value of "1," and the "clear the carry" instruction presented next, provides a convenient method for conditioning the carry flag before an arithmetic or rotate instruction.

E

Clear the Carry Flag CLC \$18

This instruction clears the carry flag by loading a "0."

Set the Interrupt Flag SEI \$78

The interrupt flag is set to a "1" by this execution. It may be considered a disable interrupt instruction since the interrupt flag disables the CPU from accepting maskable interrupts while it is set to a "1."

Clear the Interrupt Flag CLI \$58

This instruction clears the interrupt flag to a "0" condition. Clearing the interrupt flag allows the CPU to accept interrupts from the maskable interrupt line.

Interrupt flag instructions provide the programmer with a means of control when the computer may accept interrupts on the maskable interrupt line. The function of these two instructions is performed automatically when an interrupt is received. The computer automatically sets the I flag. Then, upon execution of the "return-from-interrupt" instruction (to be presented later), the I flag is returned to its initial state. Also, there may be times in a program when an operation to be performed affects data critical to the exe-

cution of the interrupt service routine. Before performing this operation, the interrupt flag should be set so that a maskable interrupt will not be accepted while the data is being changed. Once the program has completed this operation, the flag may be cleared to allow interrupts to be received.

#### Clear the Overflow Flag CLV \$B8

This instruction clears the two's complement overflow flag to a "0" and is useful in performing signed binary arithmetic operations.

# PUSH Status Register onto Stack PHP \$08

Occasionally, it is desired to save the current status flag settings. For example, a routine may determine that a value is negative. However, this information is not required by the program until other parameters are tested. This one-byte instruction may be used to store the status register on the stack. Then, when the program is ready to make a decision based on the sign of the aforementioned value, the status can be retrieved from the stack by the pull status instruction. Pushing the status register onto the stack stores the status in the location indicated by the stack pointer at the time of execution. Then the stack pointer is decremented. The contents of the status register is not affected.

## PULL Status Register from Stack PLP \$28

This one byte instruction causes the stack pointer to be incremented and the data on the stack at this location to be loaded into the status register. This is one method of restoring the status to a previously determined condition. The PHP and PLP instructions are also a convenient method of storing and restoring the decimal mode flag when calling an arithmetic routine that may change its setting.

It is often desirable to be able to shift the contents of an accumulator or memory location either right or left. In a fixed length register, a simple shift operation would result in some information being shifted right out of the register! Therefore, instead of losing

this information, the carry flag is used as an extension of the accumulator or memory location. The carry will "catch" the bit being shifted out of either the LSB for a shift to the right, or the MSB for a shift to the left.

When performing these shift operations, the condition of the bit being shifted into the register must also be considered. Depending on the application of the shifting operation, it may be desired to shift a zero, or to shift the initial contents of the carry flag, into this bit. The shifting operation that shifts the carry around to the opposite end of the register is termed a "rotate" operation. The initial contents of the entire register and the carry are never lost. it is shifted out one end into the carry, and from the carry back into the other end of the register.

The 6502 CPU provides four various shifting and rotating operations that may use either the accumulator or a memory location as the register to be shifted. A description of the shift and rotate operations available are presented here. Those designating an accumulator require one byte, those using the zero page addressing mode require two bytes, and those indicating the absolute addressing mode require three bytes. Only the X index register is valid for the indexed addressing modes.

| Arithmetic Shift Left |        |      |                   |

|-----------------------|--------|------|-------------------|

| ASL                   | Α      | \$0A |                   |

| ASL                   | ADDR   | \$06 | ZERO PAGE         |

| ASL                   | ADDR,X | \$16 | ZERO PAGE INDEXED |

| ASL                   | ADDR   | \$0E | ABSOLUTE          |

| ASL                   | ADDR,X | \$1E | ABSOLUTE INDEXED  |

The arithmetic shift left operation shifts either the designated accumulator or memory location to the left one bit. The MSB is shifted into the carry and a zero is shifted into the LSB. This operation multiplies the initial contents of the register by two. For multiple precision operations, this instruction may be used to shift the least significant byte, and the successive bytes may be shifted by using the rotate left instruction, to be described shortly. By starting with this instruction, initially it is not necessary to clear the carry flag. The C, N and Z flags are affected by this operation. The V flag is not.

|     |   | Logical Shift Right |

|-----|---|---------------------|

| LSR | Α | \$4A                |

| LSR | ADDR   | \$46         | ZERO PAGE         |

|-----|--------|--------------|-------------------|

| LSR | ADDR,X | <b>\$</b> 56 | ZERO PAGE INDEXED |

| LSR | ADDR   | \$4E         | ABSOLUTE          |

| LSR | ADDR,X | \$5E         | ABSOLUTE INDEXED  |

The logical shift right instruction shifts the designated register to the right one bit. Bit zero is loaded into the carry flag, and bit seven is loaded with a zero. This instruction is used to divide the contents of the register by two when the MSB is assumed to be part of the value and not the sign of the value. The C, N and Z flags are affected by the result of this operation but the V flag is not.

| Rotate Left |        |      |                   |

|-------------|--------|------|-------------------|

| ROL         | Α      | \$2A |                   |

| ROL         | ADDR   | \$26 | ZERO PAGE         |

| ROL         | ADDR,X | \$36 | ZERO PAGE INDEXED |

| ROL         | ADDR   | \$2E | ABSOLUTE          |

| ROL         | ADDR,X | \$3E | ABSOLUTE INDEXED  |

The designated accumulator or memory location is rotated one bit to the left by the execution of this instruction. The MSB is rotated into the carry, and the initial content of the carry is rotated into the LSB. Since this instruction forms a closed loop, it does not lose the contents of any of the bits. It may, therefore, be used to calculate the parity of the value in the register by rotating each bit into the carry and adding up the number of ones contained in the register. Rotating a multiple precision value to the left may be accomplished by initially clearing the carry and then, beginning with the least significant byte, rotating each byte once to the left. In doing so, it is essential that the instructions in between each rotate do not affect the carry flag. The status flags are affected in the same manner as with the arithmetic shift left.

| Rotate Right |        |      |                   |

|--------------|--------|------|-------------------|

| ROR          | Α      | \$6A |                   |

| ROR          | ADDR   | \$66 | ZERO PAGE         |

| ROR          | ADDR,X | \$76 | ZERO PAGE INDEXED |

| ROR          | ADDR   | \$6E | ABSOLUTE          |

| ROR          | ADDR,X | \$7E | ABSOLUTE INDEXED  |

The rotate right instruction rotates the designated accumulator

or memory location once to the right with the LSB rotated into the carry, and the initial contents of the carry rotated into the MSB. The parity of the register contents also may be checked by a series of rotate right instructions. Dividing a multiple precision value by two may be accomplished initially by clearing the carry and then, beginning with the most significant byte and working down to the least significant byte, each byte of the multiple precision value is rotated once to the right. Here again, the instructions in between rotate instructions must not affect the carry. The status flags are affected in the same manner as with the arithmetic shift left instruction.

## The No Operation Instruction NOP \$EA

The no operation, or NOP, instruction directs the computer to consume time by executing a machine cycle that effectively does nothing except advance the program counter to the next memory address. None of the CPU registers are affected by the operation. The instruction is useful for creating time delays, or as a filler if patches to a program are required (or anticipated).

The instructions discussed so far have been direct action ones. The programmer arranged a sequence of these instructions in memory. When the program is started, the computer proceeds to execute the instructions in the order in which they are encountered. The computer automatically reads the contents of the memory location and executes the instruction it finds there. Then it automatically increments a special address register called a "program counter" to the next sequential memory location. Often it is desirable to perform a series of instructions located in one section of the memory and then skip over a group of memory locations to start executing instructions in another section. This action can be accomplished by a group of instructions that will cause the CPU to jump to a new section of the memory and continue executing instructions sequentially from the new memory location.

There are a series of conditional branch instructions available in this computer that add considerable power to the machine's capabilities. The computer can be directed to test the status of a particular flag. If the status of the flag is the desired one, a branch will be performed. If it is not, the computer will continue to execute the next instruction in the current sequence. This capability provides a means for the computer to make decisions, and to modify its op-

eration as a function of flag status.

All of the branch instructions use the relative addressing mode to define the memory location from which the next instruction to be executed is to be taken. This mode of addressing requires two bytes of memory to properly define the instruction. The first byte contains the machine code for the type of branch instruction to be executed. The second byte contains the relative displacement, in two's complement form, from the memory location following the second byte of the branch instruction. Refer to the beginning of this chapter to review the relative addressing mode if necessary. These branch instructions do not affect any of the status flags.

The following is a list of branch instructions. Each tests a single flag to determine whether to branch, or to fall through to the next sequential instruction. The first column contains the mnemonic representation for the instruction, the second column contains the machine code for the first byte of the instruction, and the final column indicates the flag tested and the condition that would cause the instruction to branch.

| BCC  | RELA | \$90 | C=0 |

|------|------|------|-----|

|      |      | •    |     |

| BCS  | RELA | \$B0 | C=1 |

| BNE  | RELA | \$D0 | Z=0 |

| BEQ  | RELA | \$F0 | Z=1 |

| BPL. | RELA | \$10 | N=0 |

| BMI  | RELA | \$30 | N=1 |

| BVC  | RELA | \$50 | V=0 |

| BVS  | RELA | \$70 | V=1 |

## The Jump Instruction ADDR \$4C ABS

| JMP | ADDR   | \$4C | ABSOLUTE |

|-----|--------|------|----------|

| JMP | (ADDR) | \$6C | INDIRECT |

The jump instruction always results in the computer going to the designated address rather than fetching the next instruction from the current sequence. However, the jump instruction is not limited to an area in the memory relative to its current location. Using either of the addressing modes indicated, the jump instruction can direct the computer to any location throughout its memory. For the three-byte absolute addressing mode instruction, the second byte contains the low portion, and the third byte contains the page portion of the address to which the computer is to jump. For the indirect mode, the operand points to the location where the

actual address to jump may be found. The indirect pointer points to the low portion of the address and the next successive memory location contains the page portion. These jump instructions do not affect any of the status flags.

Quite often, when a programmer is developing computer programs, he will find that a particular algorithm can be used many times in different parts of the program. Rather than entering the same sequence of instructions at different locations in the memory (which would not only consume the time of the programmer but would also result in a lot of memory being used to perform the same function), it is desirable to be able to put an often used sequence of commands in one section of the memory. Then, whenever this particular algorithm is required, it would be convenient to iump to the section that contained it and perform the sequence of instructions, before returning to the main part of the program. This is a standard practice in computer operations. The algorithm can be designated as a subroutine. A special instruction allows the programmer to call a subroutine. A second type of instruction is used to terminate the sequence of instructions. This special terminator will cause the program operation to revert back to the next sequential location in the memory.

When a jump-to-subroutine instruction is executed, the CPU will save the address of the last byte of the instruction call by storing it in the stack. The address in the program counter is advanced to the last byte of the subroutine call instruction. The low portion of this address then is stored in the stack indicated by the stack pointer. The stack pointer is decremented by one, and the page portion of the address is stored in the stack. Finally, the stack pointer is then decremented once more to position it for the next operation.

The return instruction that terminates a subroutine requires only one byte. When the CPU encounters a return instruction, it causes the address stored in the stack to be pulled off into the program counter. The program counter is then incremented and the instruction following the jump to subroutine is executed. The low and then page portions of the address are each pulled from the stack in the same manner that a value is pulled from the stack and loaded into an accumulator.

#### **Jump to Subroutine**

JSR ADDR

\$20

**ABSOLUTE**

This three-byte instruction directs program execution to the

address indicated by the operand. The second byte contains the low portion and the third byte contains the page portion of the subroutine's start address. This instruction does not affect the status flags.

## Return from Subroutine RTS \$60

This one byte instruction returns program execution from a subroutine to the calling program. The return address is pulled from the stack and loaded into the program counter. The program counter is then incremented and the next instruction in the initial program sequence is executed. Since no status flags are affected by the return, the result of the subroutine's operation may be passed to the calling program through the flags.

This final group of instructions deals with the software portion of interrupt operations. These instructions, along with the interrupt flag set and clear instructions presented previously, provide the 6502 with the necessary software capability to operate under interrupt control.

# Break — a Software Interrupt BRK \$00

Execution of this one-byte instruction causes the 6502 to respond in a manner similar to the receipt of a hardware interrupt. The address of the BRK instruction plus two is pushed into the stack, followed by the status register. The break flag, bit four of the status register, will be set when it is stored as an indication to the interrupt handler that the interrupt is software generated. The program counter then is loaded with the interrupt vector at locations \$FFFF and \$FFFE. This vector is the start address of the maskable interrupt routine. At this time, any hardware interrupts that occur on the maskable interrupt line will be ignored since the interrupt disable flag is also set by this instruction.

#### Return from Interrupt RTI \$40

This one-byte instruction is used at the completion of an interrupt service routine to automatically restore the flags in the status register to their initial values at the time the interrupt was received. The return address is then pulled from the stack. Execution of the program resumes at the instruction following the last one executed before the interrupt.

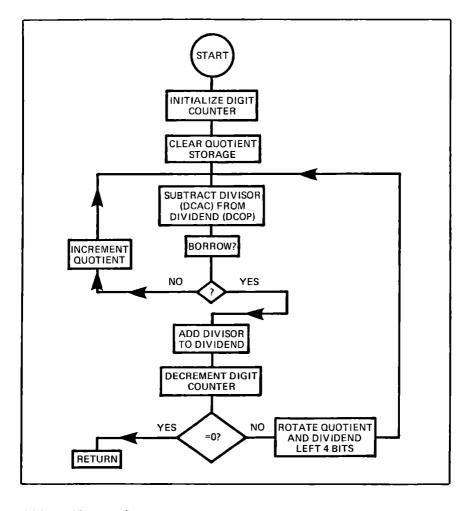

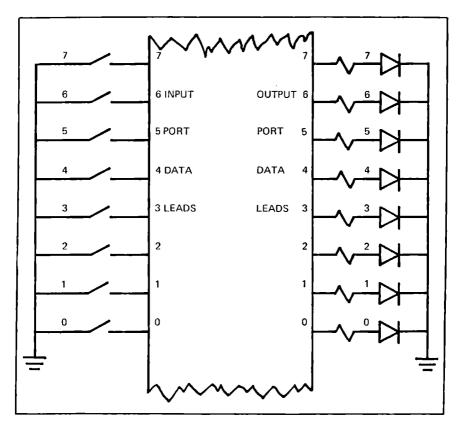

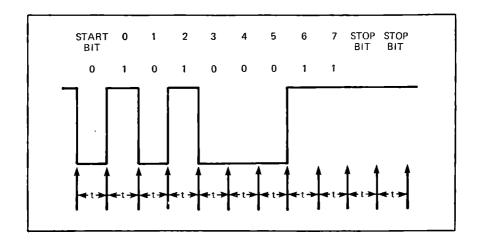

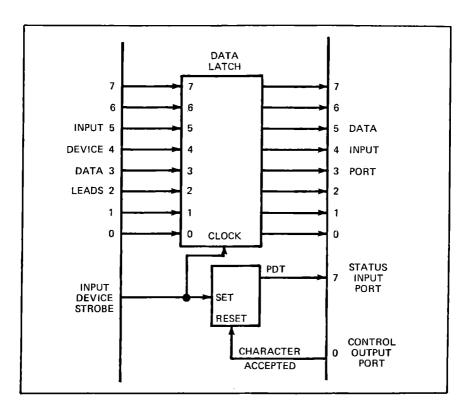

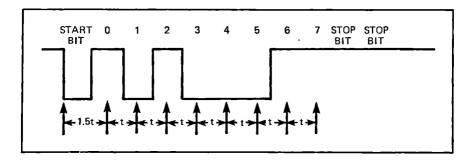

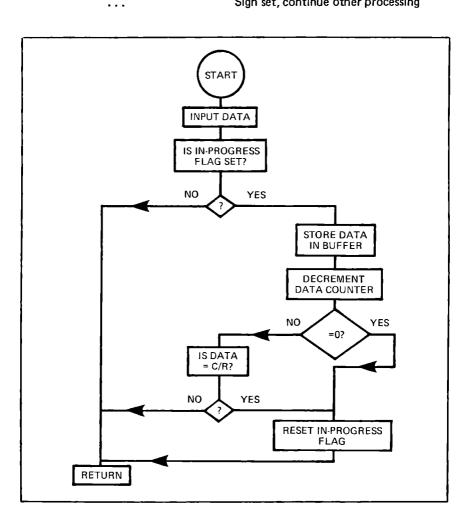

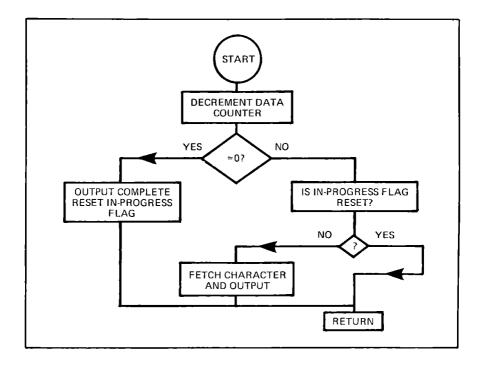

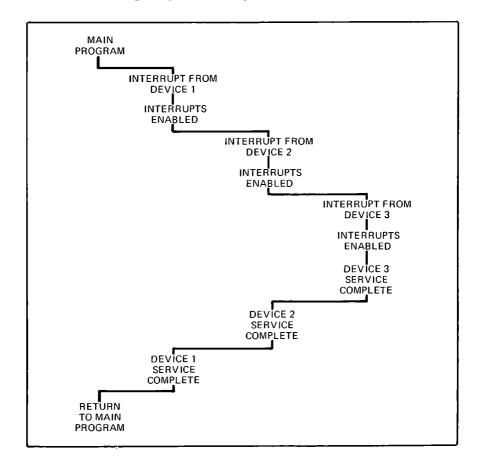

#### **Information on Instruction Execution Times**